# FinFET Based 6T-SRAM Design Using SVL Technique

Arvind Kumar Nigam M.Tech Scholar Rama University, Kanpur, India arvind nigam@rediffmail.com Shatrughan Singh

M.Tech Scholar

Rama University, Kanpur, India

makk@live.in

Raghvendra Singh Department of ECE Rama University, Kanpur, India raghav.raghvendra7@gmail.com

Abstract— The most widely used semiconductor memory types are the Dynamic Random Access Memory (DRAM) and Static Random Access memory (SRAM). Competition among memory manufacturers drives the need to decrease power consumption and reduce the probability of read failure. A expertise that is relatively new and has not been explored is the FinFET technology. In this a single cell Schmitt Trigger Based Static RAM using FinFET technology is proposed and evaluated. CMOS devices are shrinking to nanometer rule, increasing the costs in short channel effects and variations in the process parameters which lead to cause the reliability of the circuit as well as performance. To minimize short channel effects, FinFET is used. In previously proposed SVL leakage reduction techniques, SRAM are deliberate using a CMOS technology and that technique gives a 98% advantage of reducing a leakage power. The power consumption and delay is fewer for Stack and SVL technique.

Keywords—FinFET, Stack Technique, self-controllable Voltage Technique, SRAM, Short Channel Effects.

## I. INTRODUCTION

FinFETs have been proposed as a promising alternative for future technologies because of their better gate control of the channel with that of conventional bulk MOSFET. Among the different DG devices the quasi-planar structure of FinFETs device width can be increased only in quanta of the fins height and effective gate width is 2nh, where n is the number of fins and h is the fin height. FinFET is a double gate device in which second gate is connected opposite to first gate. With today's technological changes there is a huge demand for finding out devices with low power. The demand of low power becomes the key of the VLSI designs rather than high speed particularly in embedded SRAMs and catches. Static Random Access Memory which are the key elements in register files and catches are severely affected due to aging. An SRAM cell storing the same value for a large period of time undergoes highly unbalanced stress causing substantial reduction in its reliability characteristics. A SRAM cell involves of a latch, therefore the cell data is kept as long as power is turned on and refresh operation is not compulsory for the SRAM cell. SRAM is mainly used for the Cache memory

in microprocessors, mainframe computers, engineering workstations and memory in hand held devices due to high speed and low power consumption. Static Random Access Memory continues to be one of the most fundamental and vitally important memory technologies today. Each bit in an SRAM is stored on four transistors that form two cross coupled inverters. High-performance on chip caches is a crucial component in the memory hierarchy of modern computing systems[1-2].

#### II. HISTORY OF WORK

In this Work, FinFET based 6T-SRAM design using Self Controllable Voltage Level and Stack technique is targeted. The leakage power and delay is reduced by using these techniques. In the Stack technique, each NMOS and PMOS transistor in the logic gates is split into two transistors. The proposed FinFET technology and SRAM memory cell consumes low power during read and write operations compared to conventional MOSFET based SRAM design. A new leakage current reduction circuit called "improved Self Controllable Voltage Level" circuit is developed and included to reduce the leakage power of 10T SRAM. Leakage is the only source of energy consumption in an idle circuit. The main contributions of this paper are given below

- It describes how SRAM cells can be designed using FinFET technology by using Self Controllable Voltage Level Technique.

- The circuit for SVL and Stack technique is discussed.

- The simulation results of modified FinFET based 6T-SRAM using Self Controllable Voltage Level and Stack Technique[3-4].

#### III. LEAKAGE CURRENT REDUCTION TECHNIQUES

In modern high performance integrated circuits, more than 40% of the total active mode energy is consumed due to leakage currents Furthermore leakage is the only source of energy consumption in an idle circuit. FinFET SRAM arrays are important sources of leakage since the majority of transistors are utilized for on-chip memory in today"s high

ISSN NO: 2395-0730 FinFET

performance microprocessors and systems-on-chips (SoCs). The design of a low leakage FinFET SRAM cell is, therefore, highly desirable.

In addition to the leakage power issues, the degradation of data stability in FinFET SRAM cells is another growing concern with the scaling of device dimensions and voltages in each new technology generation. The FinFET SRAM cell stability is further degraded due to process variations in deeply scaled CMOS technologies.

A new FinFET SRAM cell with reduced leakage power consumption and enhanced data stability is proposed in this paper. The leakage power consumption of the new FinFET SRAM cell is reduced by 99.99% as compared to the conventional SRAM cells. The FinFET SRAM cell provides two separate data access mechanisms for the read and write operations. During a read operation, the data storage nodes are completely isolated from the bit lines, using different approach in FinFET SRAM to minimize the power[4-6].

- 1. FinFET SRAM Cell using stacking Technique,

- 2. Self-controllable Voltage Level (SVL) Technique.

#### IV. FINFET SRAM CELL USING STACKING TECHNIQUE

This improves SRAM bandwidth compared to DRAMs. A SRAM cell has three different states it can be in: standby where the circuit is idle, reading when the data has been requested and writing when updating the contents. The basic idea behind our approach for reduction of leakage power is the effective stacking of transistors in the path from supply voltage to ground. This is based on the observation made that "a state with more than one transistor OFF in a path from supply voltage to ground is far less leaky than a state with only one transistor OFF in any supply to ground path." In our method, we introduce two leakage control transistors in each inverter pair such that one of the leakage control transistor is near its cutoff region of operation. Two leakage control transistors (PMOS) and (NMOS) are introduced between the nodes and of the pull-up and pull-down logic of the inverter. The drain nodes of the transistors and are connected together to form the output node of the Inverter. The source nodes of the transistors are connected to nodes of pull-up and pull down logic respectively. The switching of transistors is controlled by the voltage potentials at nodes respectively. This wiring configuration ensures that one of the leakage control transistor is always near its cutoff region, irrespective of the input. Hence the resistance of will be lesser than it so OFF resistance, allowing conduction. Even though the resistance of is not as high as it's OFF state resistance, it increases the resistance of two ground path, controlling the flow of leakage currents, resulting in leakage power reduction. Thus, the introduction of leakage control transistors increases the resistance of the path from supply voltage to ground[6].

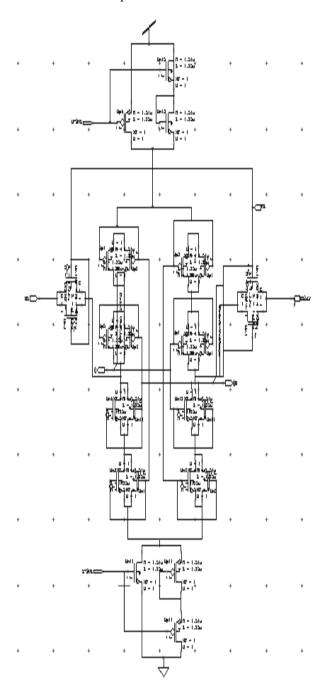

Fig.1. FinFET SRAM cell using Stacking technique

# V. FINFET SRAM USING SELF-CONTROLLABLE VOLTAGE LEVEL TECHNIQUE

A FinFET SRAM which provides low leakage power is designed in this paper. A new leakage current reduction circuit called an "improved Self-controllable Voltage Level (SVL)" circuit is developed and included to reduce the leakage power of FinFET SRAM. There are two well-known techniques that reduce leakage power (Pst). One is to use a multi-thresholdvoltage CMOS (MTCMOS). It effectively reduces Pst by disconnecting the power supply through the use of high  $V_{

m t}$ MOSFET switches. However, there are serious drawbacks with the use of this technique, such as the fact that both memories and flip-flops based on this technique cannot retain data. The other technique involves using a variable thresholdvoltage CMOS (VTCMOS) that reduces Pst by increasing the substrate-biases. This technique also faces some serious problems, such as a large area penalty and a large power penalty due to the substrate-bias supply circuits requires low leakage power[7-8].

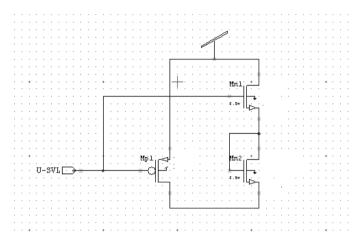

## A. Upper SVL circuit

In the above figure shows Upper SVL circuit. The impedance of a MOS transistor increases with the width of the

transistor.PMOS1 in the above circuit having width means it offers very high resistance in that path between  $V_{dd}$  and  $V_{d}$ . So that leakage in this SVL mode is very less. And also NMOS1\ and NMOS2 forms a working in normal mode of the cell.NMOS2 acts as a resister to reduce current in active mode. By connecting above way the leakage is further reduced.

Fig.2. Upper SVL circuit

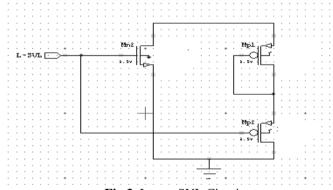

# • Lower SVL circuit

In the above circuit represents lower SVL circuit. NMOS3 work in the SVL mode and PMOS2 and PMOS3 work in the normal mode of the cell. PMOS2 acts as a resistor to reduce leakage. These two techniques reduce leakage current compared to the previous SVL.

Fig.3. Lower SVL Circuit

TABLE I. SRAM CELL SVL OPERATION

| Mode      | Upper SVL circuit                                                          | Lower SVL circuit     |

|-----------|----------------------------------------------------------------------------|-----------------------|

| Active    | PMOS switch is turned                                                      | NMOS switch is turned |

|           | on                                                                         | on                    |

|           | VDD is supplied                                                            | VSS is supplied       |

| Stand- by | NMOS switch is turned                                                      | PMOS switch is turned |

| mode      | on7                                                                        | on                    |

|           | VD( <vdd) is="" supplied<="" th=""><th>VS(&gt;VSS) is supplied</th></vdd)> | VS(>VSS) is supplied  |

The role of SVL circuits is to reduce leakage currents in standby mode or hold mode because so much leakage power in standby mode can destroy the cell. So we need to reduce that leakage. The proposed improved SVL circuits can reduce leakage more. By observing the table for inputs logic 1 and 0 to the SVL circuits we can say that the cell operates in hold mode, In this mode NMOS8 on in upper SVL circuit and PMOS4 on in lower SVL circuits to reduce the leakage [8-10].

TABLE II. SRAM CELL OPERATION WITH SVL

| 1 | u-svl | l-svl | wr | Rd | bl | blb | Qbar | q   | operation |

|---|-------|-------|----|----|----|-----|------|-----|-----------|

|   | 1     | 0     | 0  | 0  | Х  | X   | 0/1  | 1/0 | Hold      |

|   | 0     | 1     | 0  | 1  | 1  | 1   | 0/1  | 1/0 | Read      |

|   | 0     | 0     | 1  | 0  | 0  | 1   | 1    | 0   | Write 0   |

|   | 0     | 0     | 1  | 0  | 1  | 0   | 0    | 1   | Write 1   |

ISSN NO: 2395-0730 FinFET

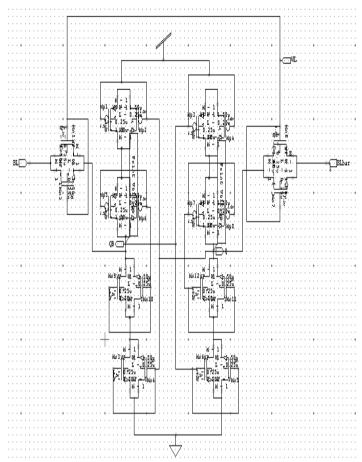

Fig.4 FinFET SRAM Cell with Normal SVL Circuits Using Stacking Technique

The above circuits work with normal SVL circuits. The circuit consists of normal FinFET SRAM cell Using Stacking Technique and upper SVL circuit and lower SVL circuits and operation of the circuit explained with the table below.

Fig.5. FinFET SRAM Cell with Improved SVL Circuits Using Stacking Technique

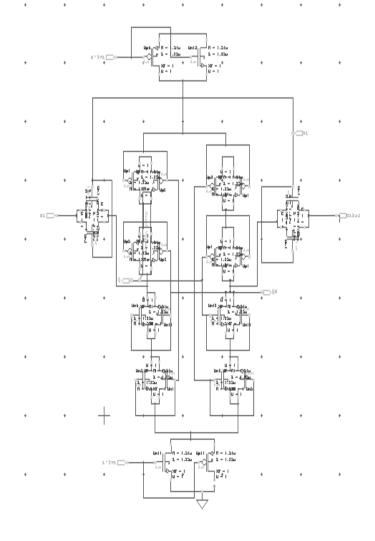

#### VI. SIMULATION RESULTS

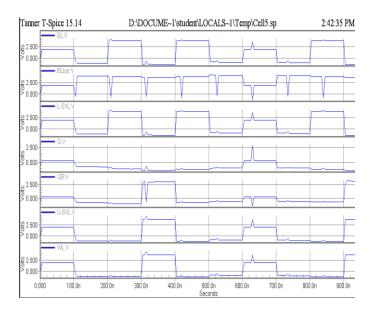

Fig.6. Simulation Result of FinFET SRAM with Improved SVL Circuits Using Stacking Technique

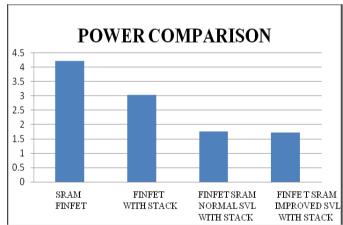

Fig.6. Power Consumption

TABLE III. POWER CONSUMPTION

| TECHNIQUE                              | POWER CONSUMPTION<br>(e-003 watts) |  |  |

|----------------------------------------|------------------------------------|--|--|

| FinFET SRAM                            | 4.210677                           |  |  |

| FinFET SRAM with Stack                 | 3.033448                           |  |  |

| FinFET SRAM Normal SVL with<br>Stack   | 1.755685                           |  |  |

| FinFET SRAM Improved SVL<br>with Stack | 1.730365                           |  |  |

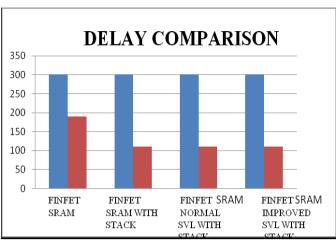

Fig.6. Delay consumption

TABLE IV. DELAY CONSUMPTION

|                                      | DELAY (Nano Second)   |                       |  |  |

|--------------------------------------|-----------------------|-----------------------|--|--|

| TECHNIQUE                            | INPUT:BLB<br>OUTPUT:Q | INPUT:BL<br>OUTPUT:QB |  |  |

| FinFET SRAM                          | 301.90472             | 190.27985             |  |  |

| FinFET SRAM with Stack               | 301.80027             | 111.01457             |  |  |

| FinFET SRAM Normal SVL with<br>Stack | 300.55516             | 110.30902             |  |  |

| FinFET SRAM Improved SVL with Stack  | 300.65293             | 110.22285             |  |  |

#### VII. CONCLUSION

Improved SVL circuit will play a major role in future. The effect of the improved SVL circuit on the leakage current through the load circuit (i.e., reduction in current) was examined. The improved SVL circuit and the load circui t were designed using FinFET technology. Sub-threshold memory design has received a lot of attention in the past years, but most of them use large number of transistor to achieve sub threshold region operation. The new technique inherently process variation tolerant, this makes the new approach attractive for Nano computing in which process variations is a major design constraint. In this circuit we have several advantages in different modes that is in operating mode high V<sub>ds</sub> to load circuits for high speed operation, in stand-by mode high Vt through -On MOS switches to load circuits for minimum stand-by leakage power, data retention, high noise immunity, small stand-by power dissipation, negligible speed degradation, negligible area overhead, high noise immunity, data retentions at stand-by mode. In this circuit the standby leakage power is reduced by which total average power also reduced and delays in FinFET SRAM Cell.

#### VIII. ACKNOWLEDGEMENTS

It gives us immense pleasure and satisfaction to express our gratitude to Dr. Harish Kumar, Professor and Dean, Mr. Raghvendra Singh and Mr. samir Kumar Mishra, Assistant Professor, Rama University, Kanpur for providing us excellent guidance and constant encouragement. A wonderful work place provided by Assistant Professor in VLSI Design Lab at Rama University, Kanpur.

#### REFERENCES

- Gavaska, K. (2013) "Design of Efficient Low power Stable 4-bit Memory cell", International Journal of Computer applications, Vol.84, No.1,pp.0975-8887.

- [2] Gavaskar, K. and Priya, S. "Design of Efficient Low power 9T SRAM Cell", P.G Scholar/VLSI Design, Assistant Professor/ECE, Bannari Amman Institute of Technology, Sathyamangalam, India.

- [3] Neha Aror, Meenakshi Suthar, and Neha Gupta (2012) "Performance evaluation of different SRAM cell structures at different technologies" International Journal of VLSI Design & Communication Systems (VLSICS), Vol.3, No.1,

- [4] Sunil Jadav, Vikrant, and Dr. Munish Vashisath, (2012) "Design and Performance analysis of Ultra Low power 6T SRAM using Adiabatic technique", International Journal of VLSI Design & Communication systems (VLSICS), Vol.3, No.3.

- [5] Ying Zhang, Sui Chen , Lu Peng and Shaoming Chen, "Mitigating NBTI degradation on FinFET GPUs through exploiting device Heterogeneity".

- [6] S.Saravanan , V.M.Senthilkumar and Aksa David, (2014), Power Reduction in SRAM- based Processor Units using 7T HETTs", International Journal of Soft Computing, Vol. 10, N.2, pp.211-217.

- [7] A.Sathishkumar and S. Saravanan, (2014) ,, Analysis and Design of Low Power High Speed Dynamic Latch

- [8] Comparator using CMOS", International Journal of Scientific and Engineering Research, Vol. 5, No.5, pp.173-177.

- [9] S.Saravanan and M.Madheswaran, (2008) "Modified multiply-accumulate architecture with switching power swiftness improvement technique", International Journal on Intelligent Electronic System, Vol.2, No.1, pp.80-85.

- [10] S.Saravanan and M.Madheswaran, (2009) "Design and analysis of a spurious switching suppression technique equipped low power multiplierwith hybrid encoding scheme", International Journal of Computer Science and Information Security, Vol.6, No.3, pp.73-78.