# Design and Analysis of Reduce Ground Bounce Noise and Low Leakage Current of Static CMOS Parallel Self Time Adder

ISSN NO: 2395-0730

Anoop Kumar Singh

M.Tech. Student

Rama University, Kanpur, India

anoop6517@gmail.com

Raghvendra Singh

Assistant Professor

Rama University, Kanpur, India

raghav.raghvendra7@gmail.com

**Abstract:** High leakage current in deep-sub micrometer regimes is becoming a significant contributor to power dissipation of CMOS circuits as threshold voltage, channel length, and gate oxide thickness are reduced. This has made power gating techniques an attractive choice for low power applications. But, this introduces ground bounce noise which is also an important challenge. So, low leakage and low ground bounce aware power gating techniques are evaluated in this paper. Techniques such as stacking power gating. Power Gating is one such well known technique where a sleep transistor is added between actual ground rail and circuit ground. The device is turned off during sleep mode to cut-off the leakage path. This technique results in a substantial reduction in leakage at a minimal impact on performance. This paper will focus on reducing sub threshold leakage power consumption and ground bounce noise during the sleep to active mode transition. The adder cells mainly focus on reduction of power and increasing of speed. For mobile applications, designers Work within a limited leakage power Specification in order to meet good battery life. The designers a part from leveling of leakage current to ensure correct circuit operation also focuses on minimization of power dissipation. In the present paper we will propose low leakage 4 bit Parallel Self Time Adder CMOS circuit in 180nm technology with supply voltage of 1V. We will perform analysis and simulation of various parameters such as standby leakage power, active power, ground bounce noise and propagation delay using Cadence aether tool with 180nm standard CMOS technology.

**Keywords**: Adder cell, Ground bounce noise, Leakage power, stacking power gating, Sleep transistor.

#### 1. INTRODUCTION

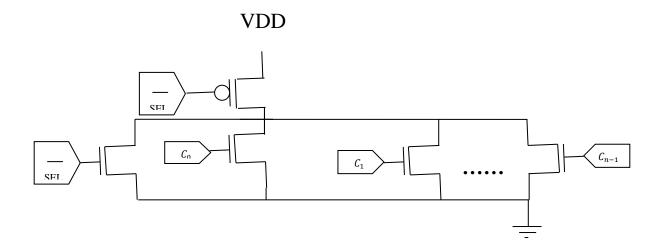

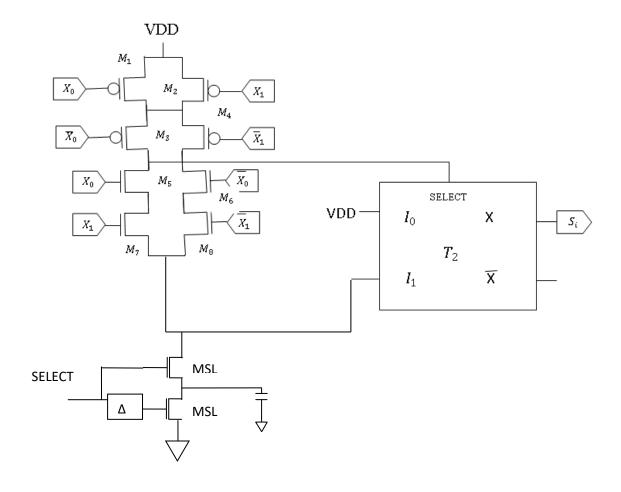

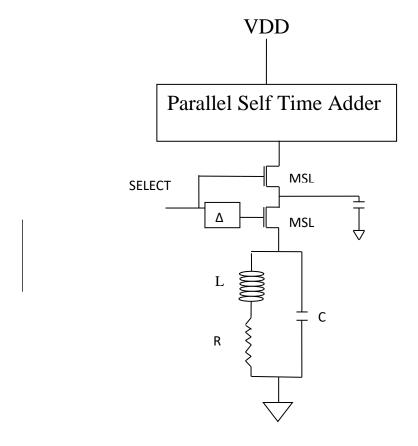

The leakage current contributes 50-60% in active power [1-2] of digital circuit. One of the most important issues in VLSI design is stand by leakage current with continuous down scaling in advanced CMOS technology. The power reduction must be achieved without trading-off performance which makes it harder to reduce leakage during normal (runtime) operation. Electronic device such as mobile phone is used commonly these days. It's battery life span is of great concern. When mobile phone is operated in standby mode, certain programs of mobile phone are turned off during active or talk mode but this doesn't stop the battery from getting depleted. In this paper, we have proposed new Parallel Self Time Adder with low power and reduce ground bounce noise based on Stacking Power Gating Technique The aim of paper is to implement the full adder to reduce power and to increase speed [3-4]. This techniques uses improvement of power efficiency and ground bounce noise reduction of the A Parallel self Time adder at 180 nm technology. Ground bounce noise [5] – [9], also known as simultaneous switching noise (SSN) or delta-I noise, is a voltage glitch induced at power/ground distribution connections due to switching currents passing through either wire/ substrate inductance or package lead inductance associated with power or ground rails. Ground bounce noise phenomenon during mode transition and leakage current in standby mode is investigated in this paper. We have seen several techniques proposed to reduce leakage power [10]. To decrease the ground bounce noise and leakage power, a modified design with the stacking power gating technique is shown in Fig. (9) and (10). In this technique stack sleep transistor is connected to the virtual ground of the circuits to reduce the magnitude of voltage glitches and current and reduction of leakage power by stacking effect, when both the sleep transistor ST1 and ST2 is turn off (sleep mode). Here with help of select input we have reduced ground bounce noise and this is achieved by the adjusting both the transistor with help of  $\Delta T$  (delay between the both sleep transistor) (sleep to active mode) [12]. Power gating uses low-leakage PMOS transistors as header switches to shut off power supplies to parts of a design in standby or sleep mode [11]. NMOS footer switches can also be used as sleep transistors.

### 2. Parallel Self Time Adder

The architecture and theory behind PASTA is presented in this section. The adder first accepts two operands to perform half-additions for each bit. Subsequently, it iterates using earlier generated carry and sums to perform half-additions repeatedly until all carry bits are consumed and settled at zero level.

ISSN NO: 2395-0730

#### 2.1 Architecture of PASTA:

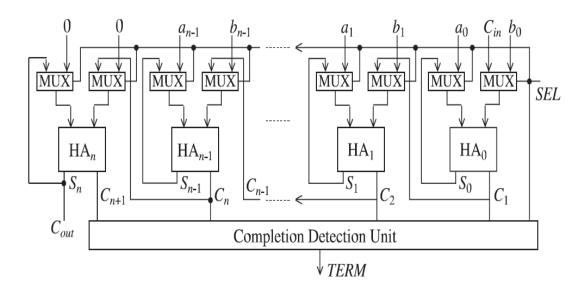

The general block diagram of the Parallel Self-Timed Adder (PASTA) is presented in Fig.1 The selection input for two-input multiplexers corresponds to the Req handshake signal and will be a single 0 to 1 transition denoted by SEL. It will initially Select the actual operands during SEL = 0 and will switch to feedback/carry paths for subsequent iterations using SEL = 1. The feedback path from the HAs enables the multiple iterations to continue until the completion when all carry signals will assume zero. The sequential circuits are often serial/chain adders and are not the match for high speed combination adder. Multi bit adders are often constructed from single bit adders using combinational and sequential circuits for asynchronous or synchronous design.

Fig1. Parallel Self Time Adder

# 2.2 State Diagram:

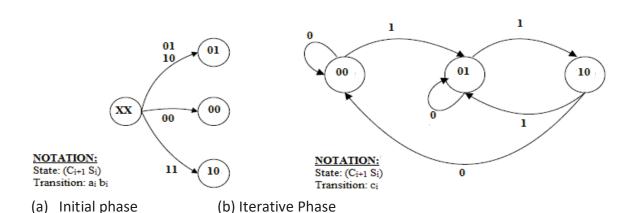

In Fig. 2, two state diagrams are drawn for the initial phase and the iterative phase of the proposed architecture. Each state is represented by (Ci+1, Si) pair where Ci+1, Si represent carry out and sum values, respectively, from the  $i^{th}$  bit adder block. During the initial phase, the circuit merely works as a combinational HA operating in fundamental mode. It is apparent that due to the use of HAs instead of FAs, state (11) cannot appear. During the iterative phase (SEL = 1), the feedback path through multiplexer block is activated. The carry transitions (Ci) are allowed as many times as needed to complete the recursion.

Figure 2: Initial and Iterative Phase State Diagrams for PASTA

# **2.3.** Implementation of Parallel Self-Timed Adder (PASTA):

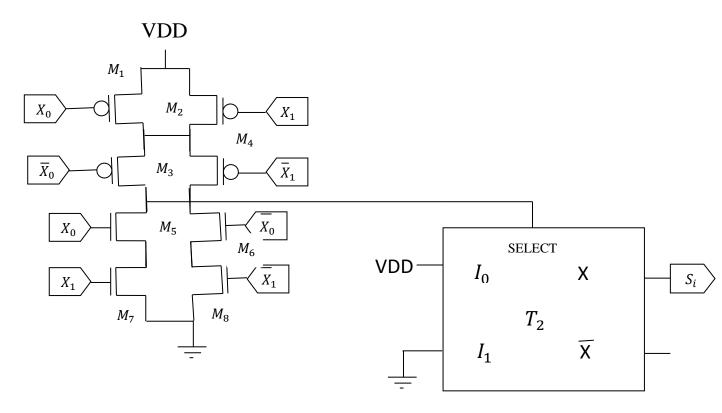

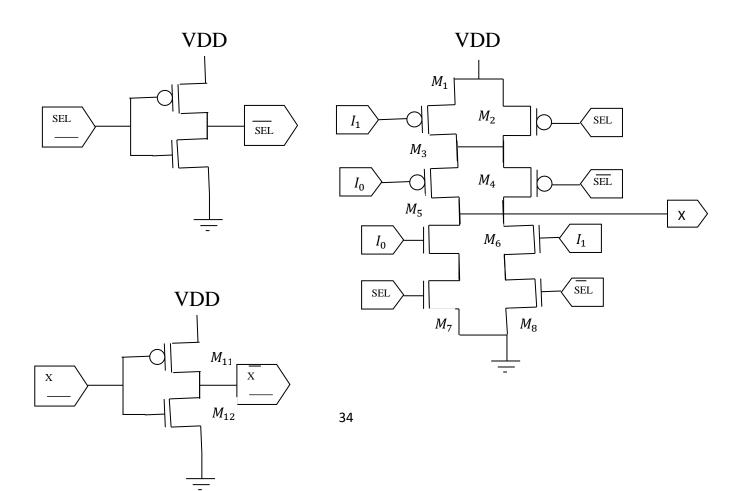

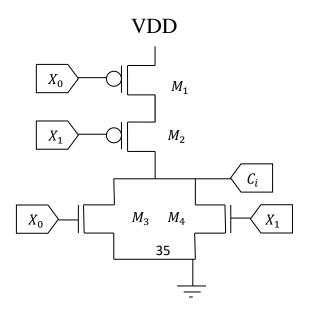

A CMOS implementation for the recursive circuit is shown in Fig. 3. For multiplexers and AND gates we have used TSMC library implementations while for the XOR gate we have used the faster ten transistor implementation based on transmission gate XOR to match the delay with AND gates [15]. An alternative more practical pseudo-nMOS ratio-ed design is used. This requires a large fan-in *n*-input NOR gate. The resulting design is shown in Fig. 3(d). The pMOS transistor connected to *V*DD of this ratio-ed design act as a load register, resulting in static current drain when some of the nMOS transistors are on simultaneously. the pseudo-nMOS design, the completion unit avoids the high fan-in problem as all the connections are parallel. The negative of SEL signal included the term signal. During the initial selection phase of the actual inputs. It is ensure that the completion can not be accidently turned on. The PMOS Pull up Transistor always on, during the duration of the actual computation a static current will flow.

Fig.3

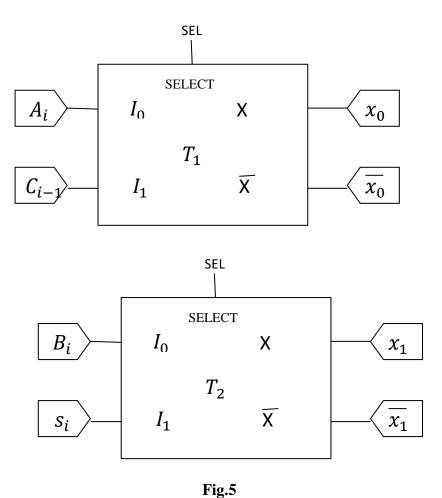

A Single bit Adder module in (fig 3, fig 4, fig 5).

Fig.6.  $(2\times1~MUX~for~1~Bit~Adder)$

Fig.7.(The Termination signal generation circuit)

## Fig.8. (A Signal Bit carry module)

In this technique, both MSL1 and MSL2 sleep transistors are turned off. Here, SELECT input is applied in such a manner that ground bounce noise is lowest and this is achieved by keeping the value of  $\Delta T$  which gives the summation of ground bounce noises of these two transistors lowest. If  $\Delta T$  is half the oscillation period of the ground bounce noise then the positive peak of the ground bounce noise lay over the negative peak there by bringing ground bounce noise closer to zero. In this technique we used the stacking sleep transistor to minimize the peak current and voltage glitches in power rails i.e ground bounce.

Fig.9.Modified 4 bit A Parallel self time Adder with forward body biased Stacking Power Gating Technique.

36

Fig.10.Modified 4 bit A Parallel self time Adder with forward body biased Stacking Power Gating Technique and ground bounce noise.

### 3. PERFORMANCE ANALYSIS AND SIMULATION

In this section, we have performed simulation of our base structure PASTA and modified PASTA adder (adder with FBB Stacking Power Gating Technique ) on Cadence aether Tool and SPECTRE Simulator at 180 nm Technology.

#### 3.1. Active Power:

The Active power is dissipated by the circuit when the circuit is operation state. Here we will calculate the active power of circuit on the basis of voltage and temperature at 180 nm technology. The Active power includes both dynamics and static power. The Active power consumption of CMOS circuit [17] [18] is described by the following equation.

ISSN NO: 2395-0730

$$P_{active} = P_{dynamic} + P_{static} \tag{1}$$

$$P_{active} = P_{switch} + P_{short} + P_{leak} \tag{2}$$

$$P = \alpha_{0 \rightarrow 1} \times C_1 \times F_{clock} \times V_{dd}^2 + I_{short-circuit} \times V_{dd} + I_{leakage} \times V_{dd} \tag{3}$$

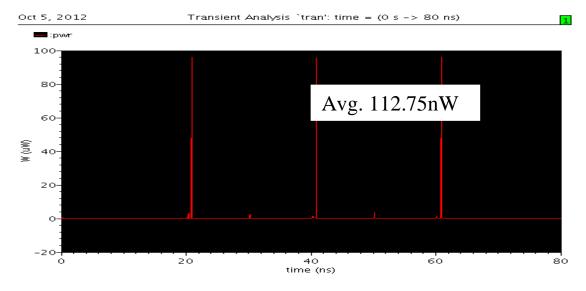

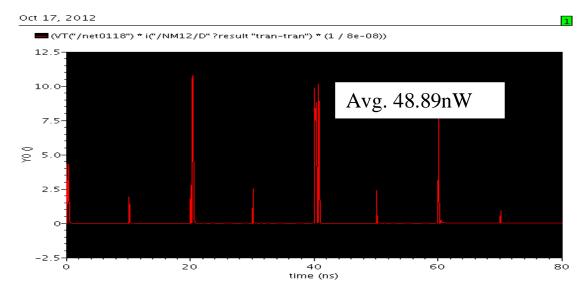

Where,  $\alpha_{0\,to1}$ = probability,  $C_1$ =load capacitance, $F_c$  =Clock Frequecy, Vdd=power supply,  $I_{short}$  =short circuit current,  $I_{leak}$  =leakage current As shown the table 1. figure(9) and (10) in the case of modified 4 bit a Parallel self time adder with forward body biased multimode MTCMOS active power is reduced compared to conventional A Parallel self time adder .The reduction almost 57.71 % at voltage 0.7 V and temperature 27° C.

**Table 1: Active Power**

| Circuit                   | Base Pasta Adder |              | Modified Pasta Adder |              |

|---------------------------|------------------|--------------|----------------------|--------------|

| Supply and<br>Temperature | .7v              | 27° <b>C</b> | .7v                  | 27° <b>C</b> |

| Active power              | 112.75           | 112.75       | 48.89                | 48.89        |

Fig.11.Active Power of conventional 4 bit PASTA

Fig.12.Active Power of Modified 4 bit PASTA

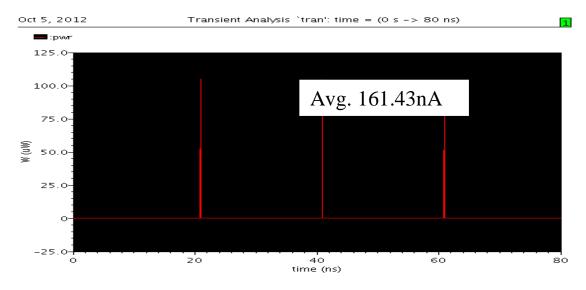

# 3.2. Stand By Leakage Current:

The stand by leakage is obtained when the circuit is in idle mode. When the leakage current measures in stacking power gating then both transistors are off [21]. Here the sleep transistor connects to the pull down network of Parallel self time adder circuit and ground of the circuit. The basic equation of stand by leakage

$$I_{leakage} = I_{sub} + I_{ox}$$

$$I_{sub} = K_1 W e^{-Vth/nV_0} \left[ 1 - e^{-\frac{V}{V_0}} \right]$$

(5)

Where,  $I_{sub} =$  threshold leakage current  $I_{ox}=$  Gate oxide current.

Where k1 and n is experimentally derived, W is gate width,  $V\theta$  is thermal voltage, n slope shape factor/ sub threshold swing coefficient,  $V_{th}$  is threshold voltage.

$$I_{ox} = K_2 W \left[ \frac{V}{T_{ox}} \right]^2 e^{-\alpha T_{ox}/V_0}$$

(6)

Where  $K_2$  and  $\alpha$  are experimentally derived, Tox is oxide thickness.

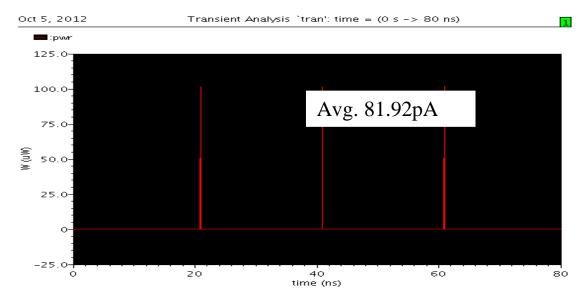

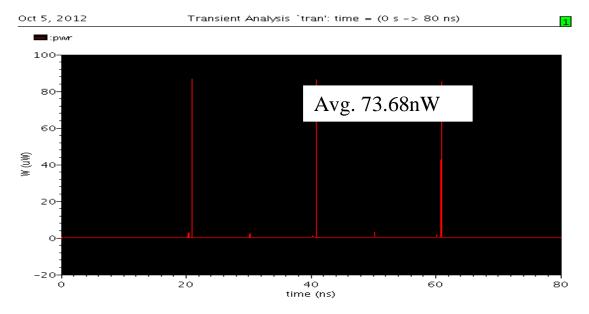

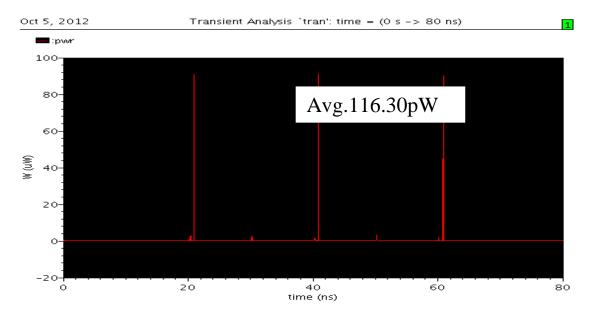

Stand by leakage current is measured by at 0.7V and 27°C. It is greatly reduced almost to 90% in modified Parallel Self Time adder with stacking power gating. The table 3, 4 and figure 13 and 14 shows the leakage current at various voltages and various temperatures.

Table 2: Stand by Leakage current and leakage power due to various voltages

| Volt(v) | Lea                   | Leakage Current           |                       | akage Power               |

|---------|-----------------------|---------------------------|-----------------------|---------------------------|

|         | Base<br>Pasta<br>(nA) | Modified<br>Pasta<br>(PA) | Base<br>Pasta<br>(nw) | Modified<br>Pasta<br>(pw) |

| 0.5     | 94.65                 | 49.67                     | 32.61                 | 103.76                    |

| 0.7     | 161.43                | 81.92                     | 73.68                 | 116.30                    |

| 0.9     | 233.49                | 160.45                    | 146.71                | 136.13                    |

| 1.1     | 284.65                | 221.20                    | 294.32                | 146.33                    |

| 1.3     | 378.78                | 402.44                    | 349.32                | 227.53                    |

Table 3: Stand by Leakage current and leakage power due to various temperatures

| Temp.°C | Leakage Current |          | Leakage Power |          |

|---------|-----------------|----------|---------------|----------|

|         | Base            | Modified | Base          | Modified |

|         | Pasta           | Pasta    | Pasta         | Pasta    |

|         | (nA)            | (PA)     | (nw)          | (pw)     |

| 27      | 161.63          | 81.65    | 73.43         | 116.43   |

| 47      | 163.32          | 142.53   | 179.54        | 258.60   |

| 67      | 165.31          | 252.71   | 81.54         | 390.26   |

| 87      | 168.55          | 322.21   | 83.54         | 446.62   |

| 107     | 196.23          | 428.01   | 93.09         | 574.16   |

# 3.3. Stand by leakage Power:

Basically the standby leakage power is the product of the leakage current and supply voltage [20]. Here when the sleep transistor is off, we measure the leakage power. The stand by leakage power is measured at the time of idle mode. The basic equation of leakage power is

$$P_{leakage} = I_{leakage} \times V_{dd} \tag{7}$$

Where Vdd=Power supply,  $I_{leakage}$  =Leakage current,  $P_{leak}$  = Leakage power. The table (3) (4) and figure 15, and 16 show that leakage power is reduced in various voltages and temperatures after applying stacking power gating. This basic concept would be utilized to improve the power performance of the adder in this paper. Lowering Vdd would significantly reduce the power consumption of the circuit. The equation shows that the power depends on different parameters as well as on supply voltage (Vdd).

. Fig.13. Leakage Current of conventional 4 bit PASTA

Fig.14.Leakage Current of modified 4 bit PASTA

Fig.15.Leakage power wave of conventional 4 bit PASTA

Fig.16.Leakage power wave of modified 4 bit PASTA

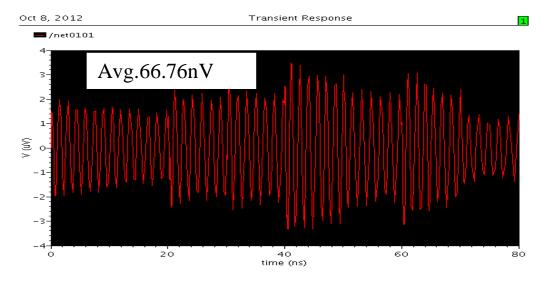

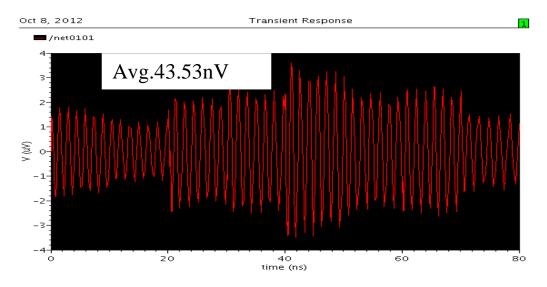

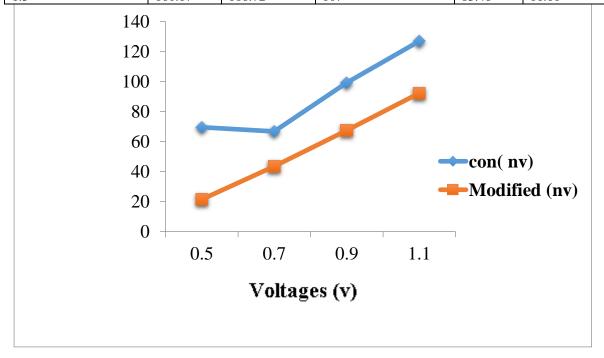

#### 3.4. Ground Bounce Noise:

There are some methods such as power gating to address the problem of ground bounce in low-voltage CMOS circuits. All the designs we are reduced the ground bounce noise using the Stacking power gating logic circuits. Ground Bounce is a voltage oscillation between the ground pin on a component package and the ground reference level on the component die. Essentially it is caused by a current surge passing through the lead inductance of the package. The effect is most pronounced when all outputs switch simultaneously. In saturation region an instantaneous charge current passes through the sleep transistor, during power mode transition. The noise depends on the voltage. The ground bounce noise model is shown in Fig (17) and (18)[22]. As shown in the table 4, and figure 19 and 20 the ground bounce noise is reduced up to 55 % in to various voltage and temperature.

Fig.17.Ground bounce noise of base PASTA

Fig.18.Ground bounce noise of modified PASTA

Table 4 GROUND BOUNCE NOISE OF 4 BITS PARALLEL SELF TIME ADDER

| Voltage(v) | Ground Be     | Ground Bounce Noise (nv) |     | Ground B      | Ground Bounce Noise (nv) |  |

|------------|---------------|--------------------------|-----|---------------|--------------------------|--|

|            | Base<br>Pasta | Modified<br>Pasta        |     | Base<br>Pasta | Modified<br>Pasta        |  |

| 0.5        | 69.54         | 21.43                    | 27  | 66.43         | 43.78                    |  |

| 0.7        | 66.76         | 43.53                    | 47  | 69.90         | 36.64                    |  |

| 0.9        | 99.21         | 67.36                    | 67  | 72.21         | 47.26                    |  |

| 1.1        | 128.86        | 92.26                    | 87  | 77.71         | 56.18                    |  |

| 1.3        | 160.17        | 118.72                   | 107 | 83.48         | 66.66                    |  |

Fig.19.Ground Bounce Noise graph of PASTA at various voltage

Fig.20.Ground Bounce Noise graph of PASTA at various Temprature

### **Conclusion:**

Standby leakage current, ground bounce noise and power consumption for stacking power gating, approaches is evaluated in this paper. and successfully reduces ground bounce noise, stand by leakage current with considerable amount. Effect of temperature on ground bounce noise and standby leakage current for different power gating approaches for high speed 4- bit parallel self time adder circuit have been also analyzed in this paper.

A stacking power gating approach has been presented which reduces peak of ground bounce noise, standby leakage current and active power dissipation. It has been evaluated that this approach reduces standby leakage current by 89.8% and active power by 80.06%. The reduction of ground bounce noise is also considerable in this approach. Ground bounce noise is also evaluated with temperature variations. Sleep transistors are kept at high threshold voltage to reduce the standby leakage current. This technique reduces the standby leakage current and active power by 96.5%, 94.95% respectively as on compared to conventional mode.

#### REFRENCES

- [1]International Technology Roadmap for Semiconductor," Semiconductor Industry Association, 2005.[Online]. Available http://public.itrs.net.

- [2] S.G.Nagendra and A.Chandkasam,"Leakage in Nanometer CMOS Technologies, New York: Springer-verilog, 2006

- [3] Pren R. Zimmermann, W. Fichtner, "Low-power logic styles: CMOS versus pass-transistor logic," IEEE J. Solid- State Circuits, vol. 32, pp. 1079–1090, July 1997.

[4] Tripti Sharma, K.G.Sharma, Prof.B.P.Singh, "High Performance Full Adder: Cell: Comparative Analysis", Proceedings of 2010 IEEE Students' Technology Symposium, IIT Kharagpur, 3-4 April 2010.

ISSN NO: 2395-0730

- [5] Rabaey J. M., A. Chandrakasan, B. Nikolic, *Digital Integrated Circuits, A Design Perspective*, 2<sup>nd</sup> Prentice Hall, Englewood Cliffs, NJ, 2002.

- [6] Pren R. Zimmermann, W. Fichtner, "Low-power logic styles: CMOS versus pass-transistor logic," *IEEE J. Solid-State* Circuits, Vol. 32, pp. 1079–1090, July 1997.

- [7] "International Technology Roadmap for Semiconductors," Semiconductor Industry Association, 2005. [Online]. Available: http://public.itrs.net.

- [8]Shilpi Birla, Neeraj K. Shukla, Manisha Pattanaik and R.K Singh "Analysis of the data stability and leakage reduction in the various SRAM cells topologies", International Journal of engineering science & technology computer (IJEST), Singapore, vol. 2(7), 2010, pp. 2936-2944, ISSN: 0975-5462.

- [9] M. Tie, H. Dong, T. Wong, Xu Cheng, "Dual- Vth leakage reduction with fast clock skew scheduling enhancement", IEEE conference on Design Automation & Test in Europe, 2010, pp. 520-525. [10]Tripti Sharma, Prof.B.P.Singh, K.G.Sharma, Neha Arora Electronics & Communication Deptt. MITS Deemed University, Rajasthan INDIA, "High Speed, Low Power 8T Full Adder Cell with 45% Improvement in Recent Advances in Networking, Threshold Loss Problem", VLSI and Signal Processing. [11]G.Shyam Kishore,"A Novel Full Adder with High Speed Area" Low National Conference Information and Communication Technology, IEEE, 2011. on [12] Sayan Chatterjee et.al [2015] Study and Analysis of Full Adder in Different Sub-Micron Technologies with an Area Efficient Layout of 4-Bit Ripple Carry Adder in International Journal of Innovative Research in Computer and Communication Engineering (An ISO 3297: 2007 Certified Organization) Vol. 3, Issue 6, June

- [13]Kallepelli Srikanth, M. Swetha "Power Delay Analysis of Parallel Self-Timed Adder by Recursive Approach" *International Journal of Research in Advent Technology, Vol.3, No.7, July 2015 E-ISSN: 2321-9637.*

- [14]Mohammed Ziaur Rahman, Lindsay Kleeman, and Mohammad Ashfak Habib IEEE TRANSACTIONS ON VERY LARGE SCALE INTEGRATION (VLSI) SYSTEMS, VOL. 23, NO. 1, JANUARY 2015

- [15] W. Liu, C. T. Gray, D. Fan, and W. J. Farlow, "A 250-MHz wave pipelined adder in 2- $\mu$ m CMOS," *IEEE J. Solid-State Circuits*, vol. 29,no. 9, pp. 1117–1128, Sep. 1994.

- [16] J.Manohar, Ch.janardhan, Dr.K.V. Ramanaiah International Journal of Research in Computer and Communication Technology, Vol 3, Issue 9, September 2014.

- [17] Mohammad Hossein Moaiyeri and Reza Faghih Mirzaee, Keivan Navi, "Two New Low-Power and High-Performance Full Adders", Journal Of Computers, Vol.4, No. 2, February 2009.

- [18]T. Vigneswaran, B. Mukundhan, and P. Subbarami Reddy, "A Novel Low Power, High-speed 14 Transistor CMOS Full Adder Cell with 50% Improvement in Threshold Loss Problem", World Academy of Science, Engineering and Technology 13, 2008.

- [19] Manisha Pattanaik, Muddala V. D. L. Varaprasad and Fazal Rahim Khan "Ground Bounce Noise Reduction of Low Leakage 1-bit Nano-CMOS based Full Adder Cellsfor Mobile Applications", International Conference on Electronic Devices, Systems and Applications (ICEDSA) 2010, pp. 31-36.

- [20] Neil H.E.Weste, David Harish and Ayan Banerjee,"CMOS VLSI Design:A Circuit and System Perspective", Pearson Education, Third Edition 2011.

- [21] R. Bhanuprakash, Manisha Pattanaik and S. S. Rajput, "Analysis and Reduction of Ground Bounce Noise and Leakage Current During Mode Transition of Stacking Power Gating Logic Circuits",IEEE Region 10 Conference TENCON 2009, pp. 1-6.